- 标准创新

by Pete Starkey

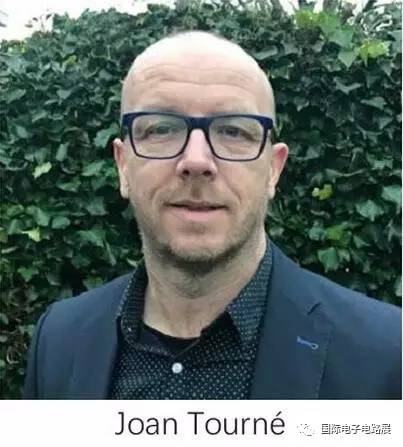

Tourné在高端PCB技术方面有长期从业背景,他在荷兰Mommers Print Service公司担任了多年的技术指导,之后去了Viasystems公司出任技术和业务总监一职,鉴于他强大的专业背景,我很好奇他的最新业务是关于什么的。

在之前的谈话中,我了解到Joan Tourné正在研究一种新型高密度互连概念。我一直找机会想和他深入探讨一下这项技术的各个细节,在他告诉我他的专利已经获得认可,所以他可以公开谈论VeCS(垂直导电结构)的时候,我十分高兴。垂直导电结构设计是为了给细间距栅格阵列组件的复杂性扇出提供一个低成本替代方案。

Nextgin Technology BV公司概况

Nextgin是一家荷兰的无晶圆厂公司,秉承着“勇于实践、梦想成真”的宗旨,这家公司在设计制造高端电路方面有着丰富的经验。我们正在为需要提高产品性能或降低产品成本的半导体封装和印制电路板行业的合作伙伴研发互连解决方案。现阶段我们在数据通讯、电信和数据处理市场中挑选出一小部分OEM,与他们合作设计并检测我们的VeCS技术。

VeCS的研发原理以及可替代性PCB概念

现有的HDI技术中最大的局限性就在于垂直互连的密度,这种密度可以在略过逐次积层(SUB)中许多步骤的情况下实现。栅格阵列封装在推动着PCB复杂性的发展,而PCB制造技术却发展迟缓。通孔技术占据了大量空间,可眼下我们已经没办法让通孔间距再缩小了。逐次积层(SUB)这一解决方案的成本相当高,而且随着积层的复杂性不断增加,产量也会随之减少。微间距栅格阵列导体分布的难度也在不断加大,这也大大限制了封装的发展。封装内核里电力分配的难度也越来越大,成本在不断提高。

“垂直导体结构”突破局限

我们不仅能通过在较小空间内装入更多垂直连接来实现更高的互联密度,同时还能提高栅格阵列组件底下的导体分布密度。完成这些不需要减少导线的线宽和间距,这样就能利用更好的信号层和更高的栅格阵列封装内外载流,来维持高传输速度以及增强信号完整性。也正因为我们没有使用逐次积层(SUB)技术,成本也随之降低。

VeCS关键特点

VeCS基于一种特殊形成的孔。这种孔相较通孔和微孔,可以用更小的空间连接到多个内层,给诸如BGA之类的阵列组件下方区域的导体分布腾出更多空间。举个例子,间距为0.65 mm的BGA能成功使用VeCS布置,相比传统通孔扇出是不可能实现的。VeCS对接地、电源层和参考层造成的干扰更少,结合传统通孔技术,就可以在BGA下面减少到只剩几个铜片。目前,我们在生产中使用的试验模型孔距为0.4 mm,使用的是单层层压工艺。

VeCS技术原理及优势

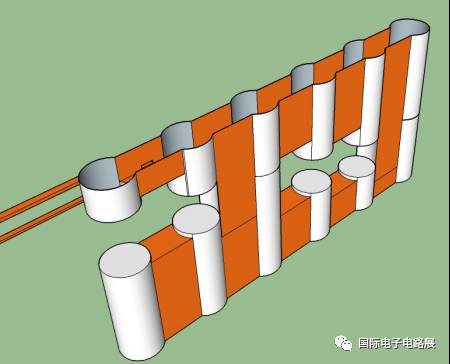

有好几种方法可以选择,最基础的一种:钻一排紧挨着的孔,直径范围在0.1 mm到0.5 mm之间,然后用材料细网将这些孔隔开。再使用钻孔、铣削或激光切割的方式把这些材料网移除,为了实现最佳配准,整个过程最好在同一台机器上进行。整个结构一旦形成,就用标准PCB工序对其进行清洗、金属化和电镀,之后再对导线的表面进行成像和蚀刻。最后,通过钻孔将电镀孔里的铜选择性移除,留下垂直的铜作为导电路径。其与传统的通孔互连的区别在于:这种孔被一条垂直的导线或半圆体代替了。垂直的导线更利于信号传导的完整性。根据不同的应用方式,这种结构可以被填孔或外层电镀。在给定的表面区域可以建立更多的垂直连接,为了控制阻抗,信号导线和接地导线可以在孔内设计成相对的样式。另外一个优点是垂直导线间不存在CAF路径。

从PCB制造商的角度来,VeCS技术优势不需要大量的资本投资或十分不同寻常的工艺化学,在适当的培训和获得执照后,任何高端线路板工厂的现有生产能力都可以应用这项技术。

图1:VeCS示意图

VeCS技术成本控制

通过更有效利用导体的分布空间,减少了线路板的层数,从而降低了成本。我们提供设计分析服务,来证明VeCS可以帮助你的产品节省多少成本。随着对昂贵材料使用的增加,降低BOM(物料清单)上的成本变得越发重要。去年的多项分析调查显示,我们能将成本降低15%到40%。

VeCS技术远景

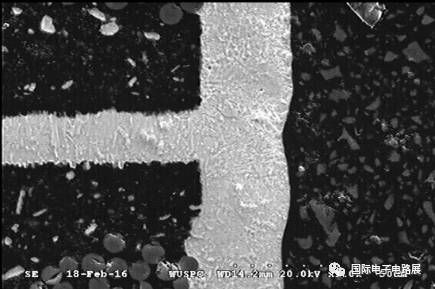

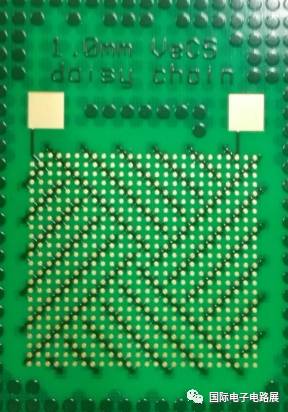

自从这项技术的概念得到最初验证以来,我们取得了很大的进步,我们还会继续与各大OEM和制造商密切合作。这里分享一个制造实例:MEGTRON6上一个层厚为2.2 mm的12层测试板,分布着直径为0.5 mm, 0.75 mm, 0.8 mm 和1.0 mm 的BGA。我们将这种结构的样品放置在288 ℃的温度下进行六次回流循环,没有发现互联失效的迹象。在288 ℃的温度下进行六次焊接冲击,得到的结果和之前相同(图2)。之后我们使用菊花链测试在制板,先进行了多次回流循环、再进行热循环直至失效,和通孔样品得到的结果相同。至于阻抗控制和信号完整性,我可以给你看看BGA下方区域一些非常好的TDR轨迹。

图2:内层互连的横截面

图3:线路板上菊花链间距为1.0mm,使用了VeCS技术,此技术用于互连可靠性测试。线路板的生产和测试由WUS(沪士)完成。

VeCS技术设计产品的能力

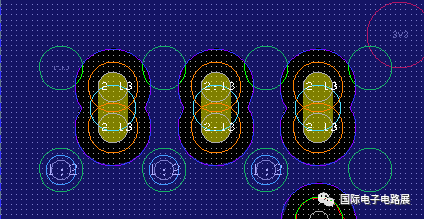

目前我们有两家CAD软件公司正在研究这项技术,并且他们已经具备了设计能力。他们已经看到了这项技术的优势并且会继续探索VeCS技术。我们还开发了一些CAD系统中的变通措施,如图4所示。虽然还需要进行一些手工操作,但我们可以展示这项技术并且能体现出VeCS的优势。我们还可以对你首选的PCB供应商进行资格培训,并且根据许可协议给OEM提供培训。

图4:Altium设计系统中的VeCS技术